Intel’s 1st Gen Core Ultra processors had a moderate to lukewarm release. Underwhelming performance, marginal efficiency improvements, and limited availability make it seem like a test drive for the 4nm-class Intel 4 process node. For gamers and enthusiasts, the “true” Core Ultra processors will launch later this year in the form of the 15th Gen Arrow Lake family. We already know the basic details of these chips, including process nodes, core architecture, and packaging. Today’s leak reveals the layout of the CPU die. [Source: Xino]

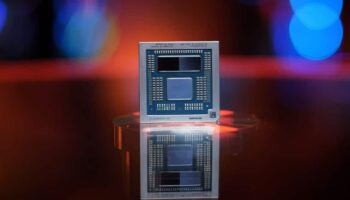

The Arrow Lake CPU tile has undergone a fraternization of sorts. With Alder, Raptor, and Meteor Lake, the P and E-core clusters are grouped separately (below). Arrow Lake spreads the quad-cluster pairs of Skymont (E) cores between columns of Lion Cove (P) cores.

It’s unclear why Intel has scattered the E-core quads between the P-cores, but it likely pertains to inter-core or memory latency. The 12th and 13th Gen processors suffer from high E-core latency. The E-cores connect through the L2 cache clusters using the L3 cache ringbus and vice versa. This adds up to inefficient figures for the outer cores. Placing the E-core clusters further apart seems counterproductive, but I suppose we’ll see.

Previous coverage on Arrow Lake:

- Intel Roadmap for 2024-25: 15th Gen Arrow Lake (20A), Lakefield (TSMC 3nm), and Arc Battlemage GPUs

- Intel 15th Gen Arrow Lake CPUs Won’t Support Hyper-Threading or Rentable Units

- Intel 15th Gen Arrow Lake CPUs to Feature Ray Tracing Cores and XMX Units for XeSS Upscaling

- Intel 15th Gen Arrow Lake CPUs Already Running in Labs, Launching in Late 2024