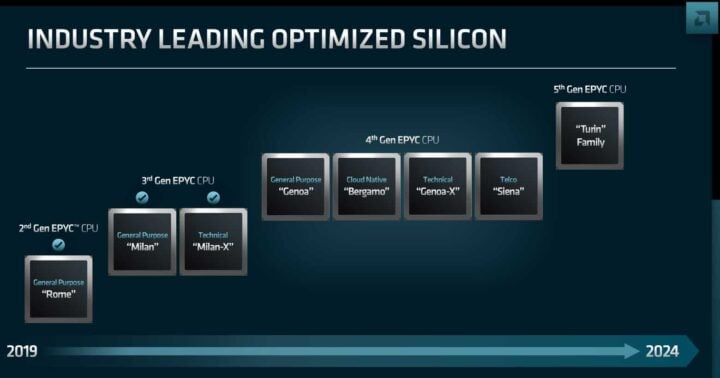

The specifications of AMD’s Zen 5 Epyc Turin processors have leaked out. Well-reputed tipster @YuuKi_AnS has shared the CPU core counts, cache, and base frequencies of the next-gen Epyc chips. Before we proceed, please note that the L3 cache numbers for the Zen 5c (Dense) variants are erroneous. To make it more confusing, the Turin Dense SKUs aren’t labeled as such and are paired with cache configurations of their hypothetical Zen 5 variants.

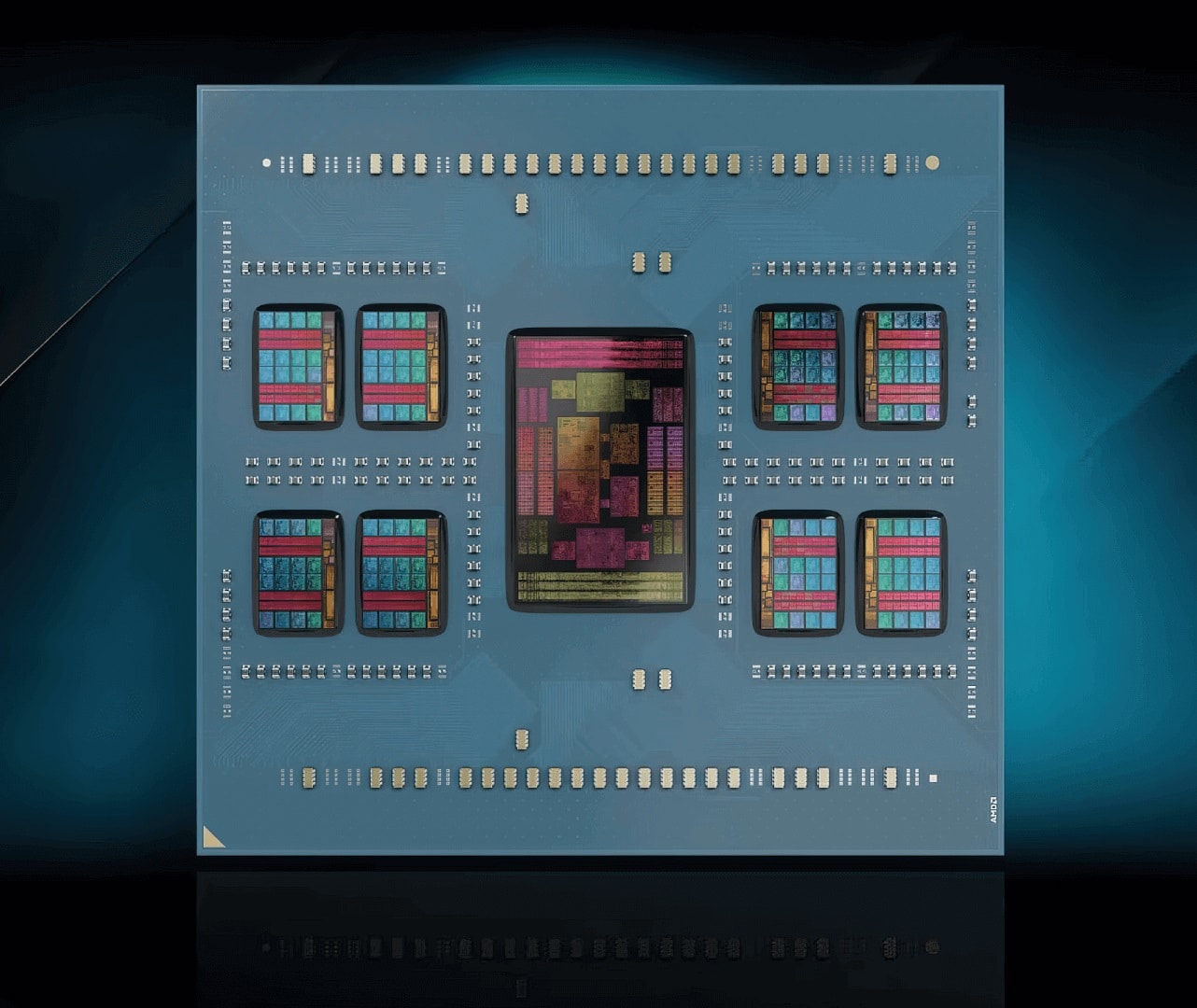

Like the Epyc Genoa family, Turin uses the SP5 (LGA-6096) socket. The Turin Classic “Zen 5” lineup will likely top out at 96 cores (192 threads) or 128 cores (256 threads) if AMD decides to be generous. The TDP of these chips will vary from 200W on the lower-end SKUs to 400W on the flagship models.

The base clocks of the LCC (lower core count) offerings hover between 3.0 GHz and 4.0 GHz. The more fleshed-out variants have stock clocks of under 3.3 GHz, with flagship models starting at 2.1 GHz. The L3 cache is unchanged at 32MB per CCD, implying a total Last Level Cache (LLC) of 384MB and 512MB for 96-core and 128-core (if it exists) variants, respectively.

The Zen 5c “Dense” family will feature up to 160 cores and 320 threads. These are clocked at just over 2GHz for the “denser” flagship SKUs with an L3 cache of up to 320MB (32MB per 16-core CCD). It looks like there will be only three Turin Dense chips with TDPs of up to 500W. Turin Classic “Zen 5” and Dense “Zen 5c” are slated to land later this year.

AMD’s Epyc Turin (Zen 5 and Zen 5c) variants will support AVX512 instructions with the classic cores allegedly featuring several 512-bit wide Floating Point Execution Units. Intel’s E-cores lack the AVX512 feature-set completely while Granite Rapids is a mystery.

For the first time in years, Intel may have a competitive server lineup to challenge AMD’s Epyc portfolio. At MWC 2024, Team Blue announced its Sierra Forest platform set to feature up to 288 cores. These E-cores will leverage the Sierra Glen architecture, an optimization of Crestmont for cloud workloads. The initial variants of SFR will pack up to 144 cores, spread across Intel 3 (3nm) chiplets alongside dual I/O dies.

Further reading: