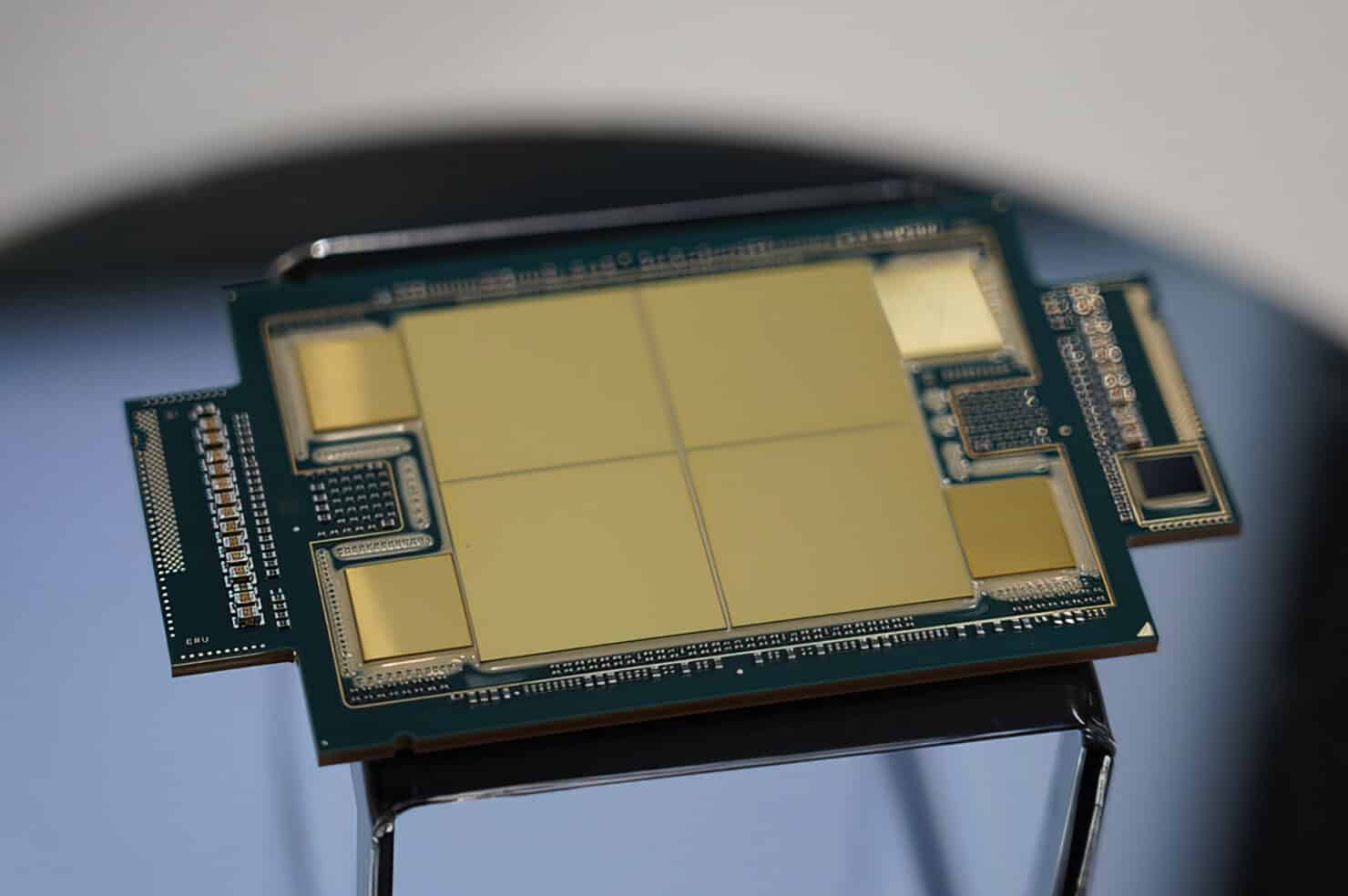

AMD’s Ryzen X3D V-Cache processors are the fastest gaming chips on the market, with up to 144MB of on-die cache. Courtesy of the vertically stacked SRAM, Team Red has delivered multiple generation upgrades within a single cycle. Till now, boost clock hikes have been Intel’s primary response to the Ryzen V-Cache threat. Together with Samsung, it is finally working on a worthy competitor to the 3D-stacked CPUs from its archrival.

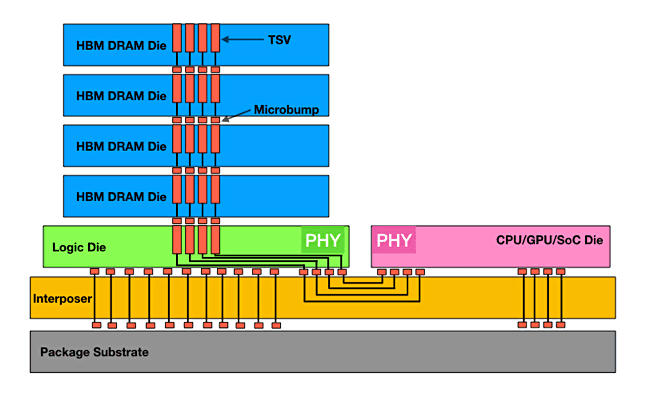

Samsung is developing its next-gen “cache DRAM” technology that may eventually replace the pricey HBM chips. An HBM package consists of multiple DRAM dies stacked vertically on top of one another, with the base die connected to the primary CPU or GPU die. HBM is known for being power efficient with low voltages and a wide bus. Historically, it has been used on GPUs, most notably data center accelerators such as the A100 and H100.

Cache DRAM utilizes a single chip with the capacity of multiple HBM dies 3D stacked directly atop the CPU or GPU compute die. Storing the necessary data closer to the processing units drastically reduces latency and efficiency. Samsung claims that cache DRAM reduces power consumption by 60% while boosting data transfer by 50% over existing HBM solutions. Currently, the dissipation of the heat generated by the 3D-stacked DRAM is the primary concern.

TSMC was able to sign multiple long-term contracts with NVIDIA and AMD thanks to its advanced 3D packaging technologies, CoWoS and SoIC. Despite having very few serious clients, CoWoS packaging capacity is fully utilized for the foreseeable future. NVIDIA’s Tensor core GPUs, alongside the Epyc Milan and Genoa-X CPUs (and soon the MI300), are tanking TSMC’s capacity.

Intel has teamed up with Samsung to apply cache DRAM to its processors and will also adopt it within its foundry, offering it to third parties. Samsung has two 2.5D packaging technologies, H-Cube and I-Cube, similar to TSMC’s FOWLP 2.5D solution. However, the cache DRAM option will leverage X-Cube 3D stacking, bolstered by an Intel collaboration, to reduce costs and expand capacity.

Mass production of cache DRAM-powered chips is expected to begin in 2025, with Intel manufacturing the first processors. NVIDIA has also shown interest in the technology and hopes to integrate it into its data center products.

Source: Naver (Via: Revengus).