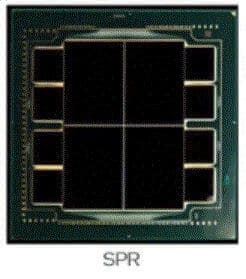

Intel’s upcoming Sapphire Rapids-SP (4th Gen Xeon Scalable) processor has been pictured, perhaps for the first time (courtesy of Tom Wassick). As you can infer from the picture, the SKU features four chiplets or tiles, each paired with two HBM2E tiles. Each die has two 1024-bit memory buses (2,048-bit overall), resulting in a width of 8,192-bit for the entire chip.

Each HBM2E pin has a bandwidth of 3.2Gbps, resulting in an overall bandwidth of 3.68 TB/s for the entire SoC. Looking at this figure, you can guess why Intel has decided to offer an HBM variant of Sapphire Rapids, or why some clients would want a custom HBM variant. This extra bandwidth should help boost neural network training or other AI-related workloads that move a lot of data around.

From what we’ve heard, Sapphire Rapids processors will be directly soldered to the motherboard via BGA (Ball Grid Array). As already reported, the 4th Gen Xeon Scalable processors will feature up to 56 cores, support for 8-channel DDR5 memory, and a TDP of 350W. In addition to this, they’ll also support the PCIe Gen 5 interface, CXL 1.1, Intel AMX, AVX512_BF16, and the AVX512_VP2INTERSECT instruction set.

Sapphire Rapids-SP should launch by early 2022, with shipments to select clients slated to commence by the end of this year itself.