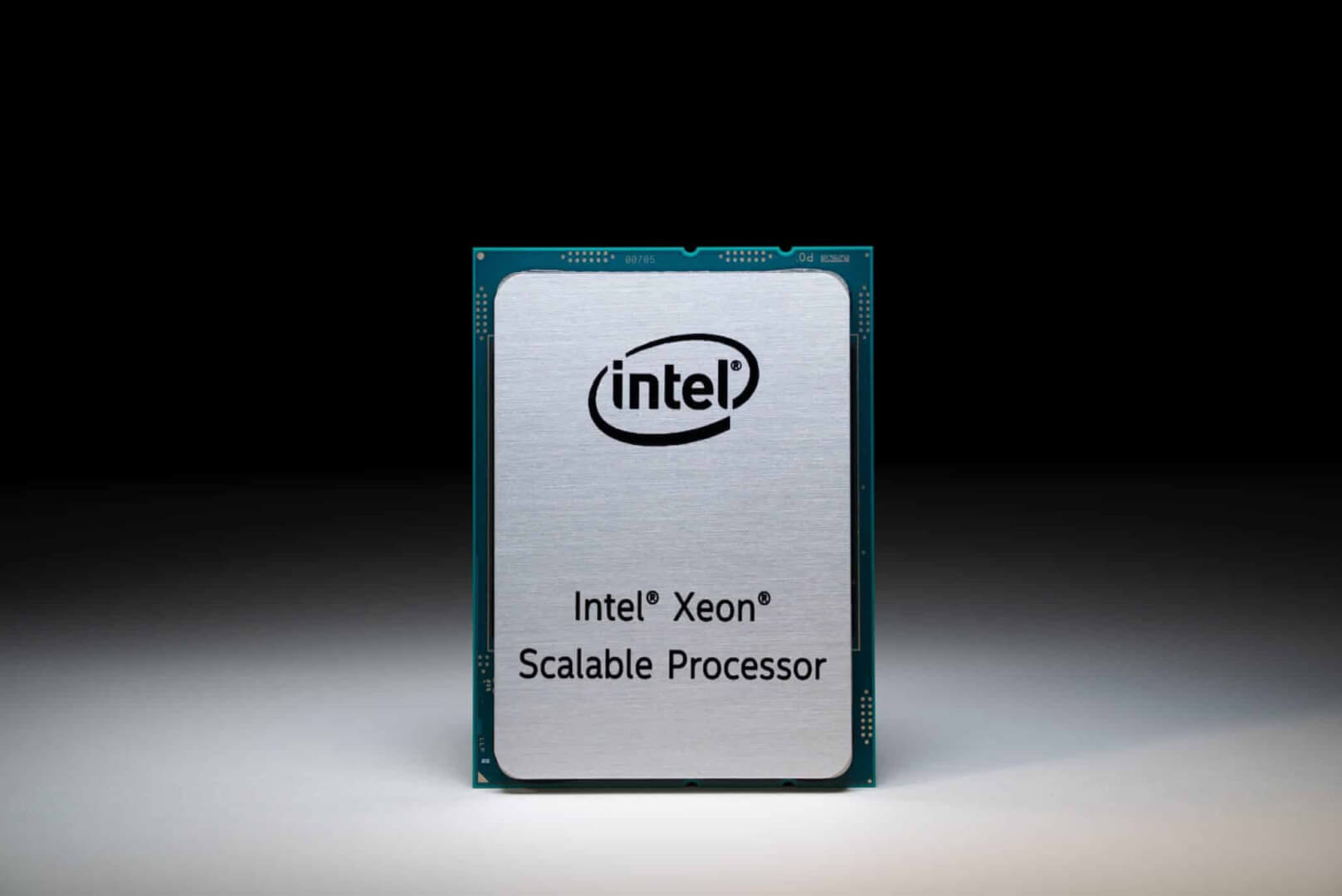

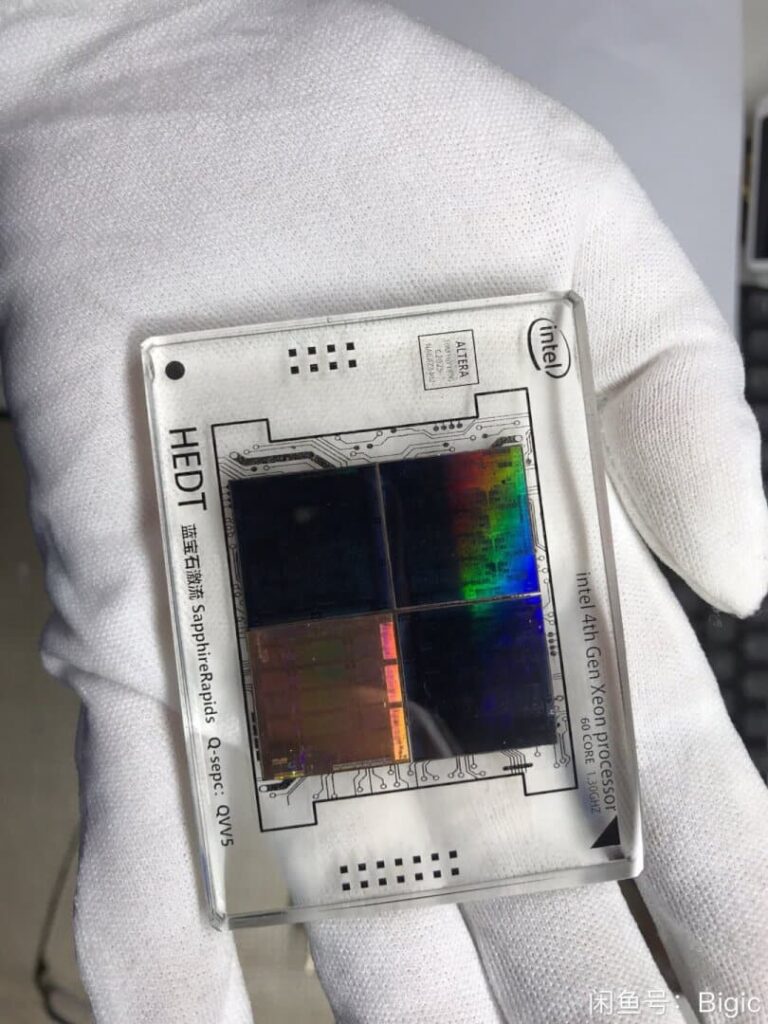

Intel’s next-gen Xeon Scalable processors will adopt a chiplet or tiled architecture for the first time in the chipmaker’s history. It’ll feature four modules or tiles, each packing up to 15 cores. One of the cores will be disabled, resulting in an overall core count of 56 for the top-end SKU.

In the above image (via: Yuuki_Ans), you can see the four chiplets or tiles expected to power Sapphire Rapids-SP. Sapphire Rapids will be based on the Golden Cove core architecture fabbed on the Intel 7 node. It’ll boast the EMIB inter-connect, and on-die HBM memory (for select SKUs), and go up against AMD’s Epyc Milan and Genoa processors. (buy zolpidem from canada) You can expect several advances in the BF16, AVX512-class instructions along with native support for DSA and AMX. It’ll feature DDR5 memory, PCIe Gen 5, as well as CXL 1.1.