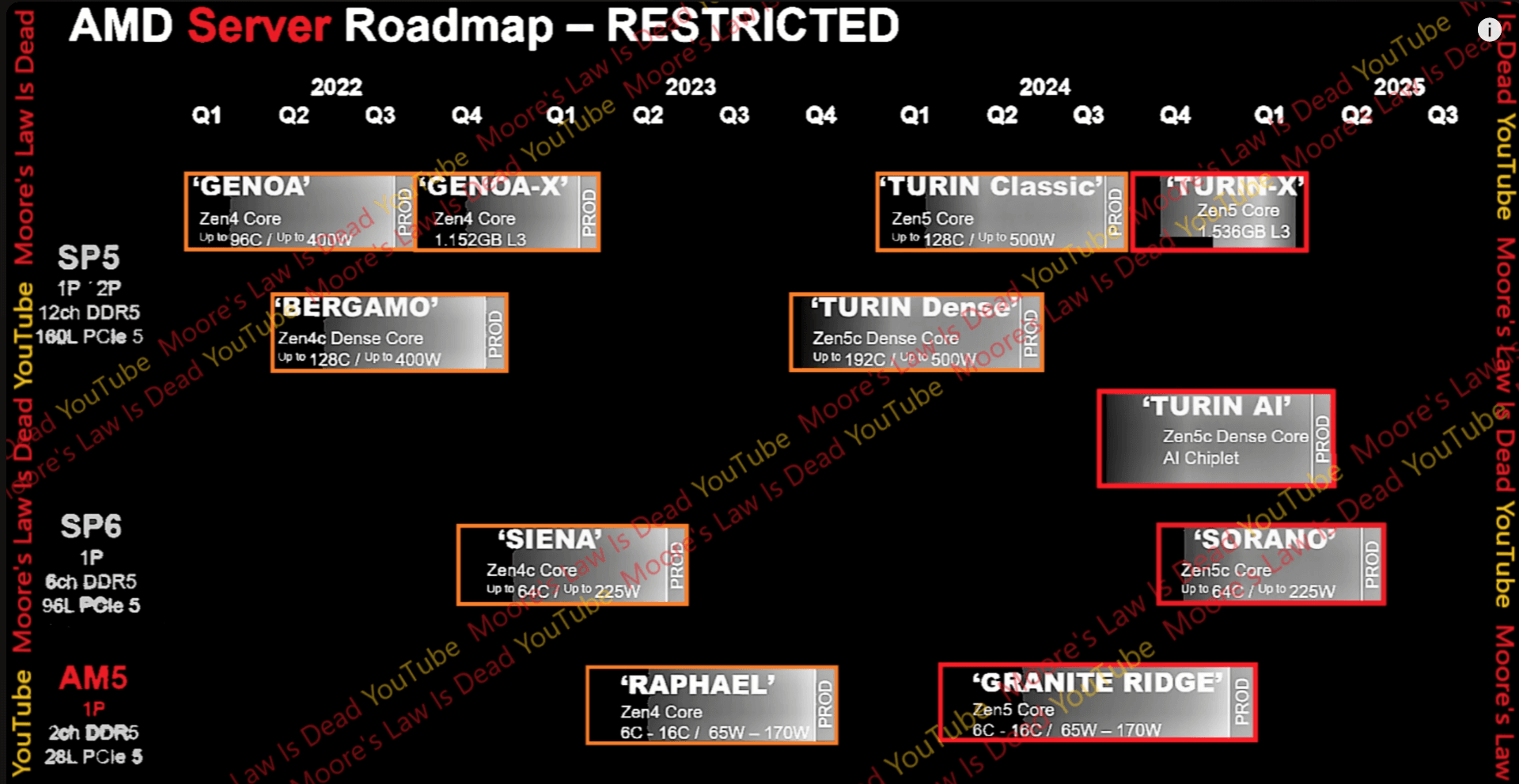

AMD’s next-gen Zen 5 Epyc processors have leaked out. Earlier today, Moore’s Law is Dead shared the block diagrams of Epyc Turin and Turin Dense. These include the core counts, CCD configuration, L3 cache, and the I/O Die specifications. From what we can glean, the Zen 5-based Epyc “Turin” processors will retain the 8-core CCD, packing up to 16 of them. This gives us a core count of 128 Zen 5 cores and 512MB of L3 cache (32MB x16).

The I/O die will feature notable upgrades, including CXL 2.0, Infinity Fabric Gen 3, and DDR5-6000 memory support. While DDR5-5600 has already been validated, DDR5-6000 is the target memory speed. Turin and Turin Dense are expected to share the same IOD. For the former, a launch target of 1H 2024 is being targeted.

Turin Dense will pack up to 16 core Zen 5c CCDs, each containing 32MB of L3 cache. A maximum of 12 Zen 5c CCDs will be squeezed onto the SP5 socket, bringing the core count up to 192 and the L3 cache to 384MB. These cloud-centric chips are expected to launch in the second half of 2024.

Further ahead on AMD’s roadmap, we’ve got Turin-X, Turin AI, and Sorano lined up for Q4 2024 and Q1 2025. Turin-X is the V-Cache version of Turin, boasting an L3 cache of 1.536GB. Turin AI will feature the Zen 5c cores paired with one or more AI chiplets. Sorano will be the low-power variant of Zen 5c, succeeding Sienna sometime in early 2025.