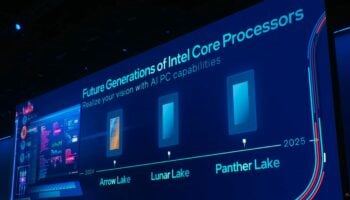

Intel adopted a hybrid core architecture with its 12th Gen Alder Lake CPUs, further fortifying it with the 13th Gen Raptor Lake family. However, these chips have failed to solve the problems that they set out to solve in the first place. They are nowhere as power efficient as rival AMD’s Ryzen 7000 notebook processors. To avoid making the same mistakes on the road to a heterogeneous design, Team Red plans a much simpler and safer route.

David Mcfee, AMD’s Corporate VP and GM of the Client Division shared the company’s strategy (via TomsHardware) on the shift to a hybrid core design. Calling Intel’s dual ISA design with varying cache and execution capabilities superfluous, he stated that AMD is looking at an alternate approach.

What McAfee is essentially talking about here is application compatibility and IPC parity. Having two different ISA (Instruction Set Architectures) makes OS-level optimization difficult, leaving a lot of performance on the table while eroding the power efficiency as well. Having a uniform architecture throughout minimizes scheduler related issues that tend affect Intel’s 12th and 13th Gen CPUs (For example, video games).

What I will say is this, I think the way that we think about it, the approach of two very different performance and efficiency cores with very different ISA support and IPC and capability is not necessarily the right approach. I think it invites far more complexity around what can execute where, and as we’ve looked at different options for core design, that’s not the approach that we’re taking.

I think as we roll more of this out over time, what you’ll see from us is an approach that takes into consideration the advantages that different core targeting can provide, but doing it in a way that’s much more, from an application perspective, much more homogeneous.

ISA, first of all, keeping that consistent to where a workload can operate on any core, has dramatic advantages. And even when you look at a Ryzen desktop CPU today, the way that the Windows scheduler is plumbed, the ability to identify cores that are faster, slower, etc., and steer threads to different cores depending on the ranking or capability within a CPU; That’s a well-established technique that we’ve used for quite some time. This then leads to, in our opinion, using a mechanism where the capability of the cores is more consistent.

David McAfee, GM and VP of AMD’s Client Division.

This is a far more tried and true way to look at bringing multiple different core targeting types into a design. I think the Intel approach invites a lot of complexity into the way that it operates. And I think our analysis has been that. I don’t think you’ll see us go down that path in the same way they have, if and when it comes to a Ryzen processor.

AMD is slated to launch its Epyc Bergamo processors in the coming weeks. These chips leverage the Zen 4c core, a stripped down variant of the Zen 4 core with all the same instructions and IPC numbers. The only difference between the two boils down to the cache. The Zen 4c reduces the L3 cache to save die area to squeeze in more cores. This strategy is effective for compute-intensive workloads.

Strix Point, AMD’s first hybrid core Ryzen processor should feature Zen 4c or a modified variant of the Zen 4 core to improve efficiency while keeping the ISA identical. As of now, AMD isn’t particularly interested in the hybrid core architecture. Their first heterogenous Ryzen CPUs should land with Zen 5 sometime in 2024 or 2025.