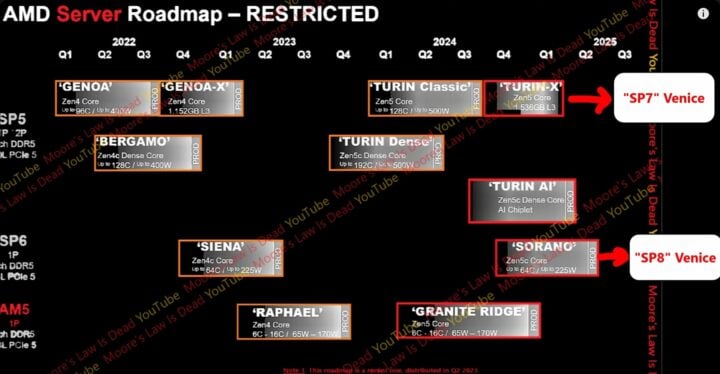

The first AMD Zen 6 leaks are here. Succeeding Zen 5 in 2025-26, these chips will focus on modularity, I/O, and core density. These early details come from “Moore’s Law is Dead,” who has proved quite reliable with previous data. First things first. We expect the first Zen 5 SKUs to land in the second quarter of 2024, followed by the Zen 5c variants later that year. Today’s data primarily deals with the Zen 6 Epyc lineup, specifically the SP7 and SP8 Venice CPUs.

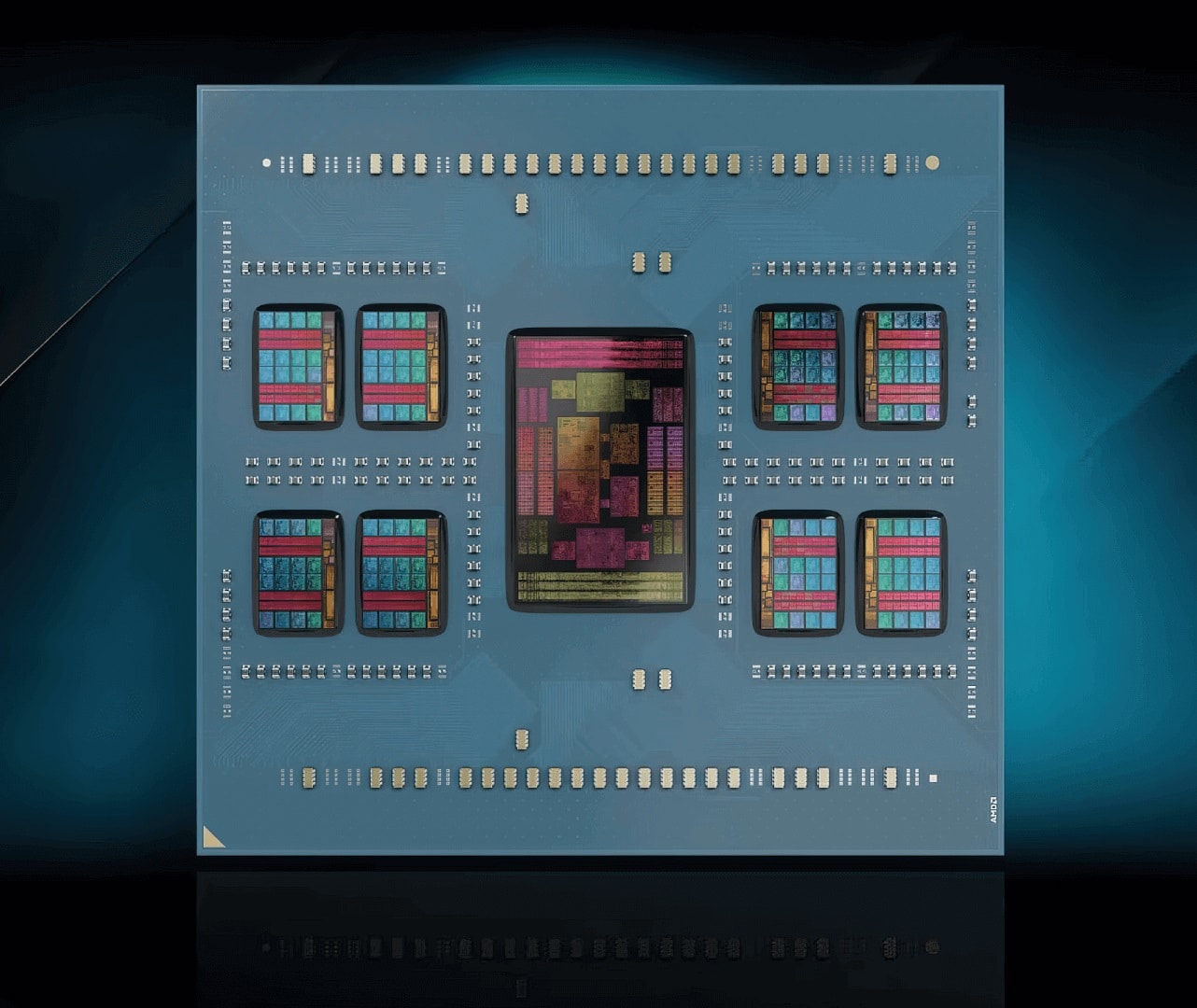

32 core CCDs and multiple IODs are the primary changes planned with Zen 6. Low and midrange processors should continue using single IODs, but higher-end and flagship will adopt multiple smaller I/O dies. For example, the 32 core variants of Epyc “Venice” will leverage a single IOD alongside a Zen 6 CCD and an NCD (Networking Compute Die). The resulting CPU would feature quad-channel DDR5-6400 memory, 32 PCIe Gen 5, and 16 PCIe Gen 6 lanes.

The 64-core Venice will feature two I/O dies, two 32-core Zen 6 CCDs and a couple of add-on dies, including NCD and FPGAs. It would offer 8-channel DDR5-6400 memory, 64 PCIe Gen 5, and 32 PCIe Gen 6 lanes. The NCD and FPGA slots can be swapped for standard CCDs or AI units per client requirements.

The “Venice SP7” flagship would feature up to 8x Zen 6 CCDs, adding up to 256 cores, 16 DDR5-6400 memory channels, 128 PCIe Gen 5, and 64 Gen 6 lanes. Each of the CCDs is expected to be fabbed on a 2nm-class node and the IOD on a 4nm derivative. As explained, each compute die can be swapped with an AI, NCD, or FPGA per the market need.

Interestingly, Zen 6c is amiss, implying that AMD has either renamed it or stopped distinguishing between them. This makes me wonder if these Zen 6 CCDs are Zen 6c designs with lesser cache or something in between. The chipmaker did something similar with its recently announced Phoneix 2 mobile processors, where it doesn’t differentiate between the Zen 4 and Zen 4c cores.

An approach lacking this differentiation is problematic as the extra L3 cache on Zen 4 substantially impacts memory-sensitive workloads like gaming. Furthermore, the Zen 4c cores are coded for much higher boost clocks than their larger sibling, resulting in a well-defined performance delta between them.