The Ryzen 7 5800X3D won’t be the only AMD SKU to feature 3D stacked cache memory. According to Greymon55 (a very well-reputed insider), the Radeon RX 7900 XT will also leverage the next-gen packaging technology to boost the LLC (last level cache). We’re likely looking at up to 256MB of L3 cache. There are several ways for AMD to do this. The cache can be 3D stacked atop the bridge interconnect or the memory controller dies, or the graphics compute dies.

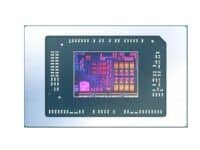

The Radeon RX 7900 XT will feature up to seven dies. Two of these will be the GCDs (Graphics Compute Dies), one I/O die (or the active bridge interconnect), and four memory/cache controller dies paired with GDDR6 memory modules.

The GCDs pack the main processing cluster across two identical dies. Each die will consist of 7,680 stream processors (cores) across 6 shader arrays and 3 shader engines. This results in an overall shader count of 15,360 spread across 12 shader arrays and 6 shader engines. The overall bus width is expected to be 256-bit with the memory controllers divided equally across the two dies.

The GCDs will be fabbed on TSMC’s 5nm (N5) node while the MCD will be fabbed on the older 6nm (N6) node. Each die should come with a 128-bit bus (divided into eight controllers), resulting in an overall bus width of 256-bit and the same external bandwidth of 448GB/s as the RX 6800 XT/6900XT.

AMD’s RDNA 3 graphics architecture is expected to get a major overhaul at the front-end, with redesigned Work Group Processors in place of Compute Units, or Dual Compute Units. With RDNA 1 and 2, the WGPs were the basic units for workload scheduling (from CUs on GCN/Vega), but it looks like that is going to change again with Navi 3x. Dual Compute Units are being discarded in favor of wider Work Group Processors, packing as many as 256 stream processors across eight 32-wide SIMDs. This means that the wave32 format of scheduling will be retained, but the number of overall active waves will be increased.