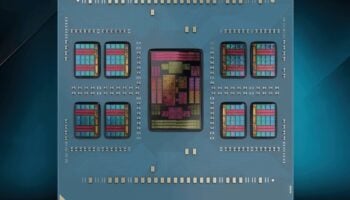

The specifications of AMD’s upcoming Milan-X server processors have surfaced. Milan-X will be the first lineup to feature 3D stacked cache (V-Cache) in the server and data center space. Intel’s Lakefield processors were the first to demonstrate the technology in the form of Foveros, but they were very limited in scope, die area, and availability. Milan-X will retain the Zen 3 core and the N7 process from TSMC, and as such, can be thought of as a special refresh or niche stack, much like the upcoming Sapphire Rapids-SP with on-die HBM memory.

According to the source (@ExecuFix), Milan-X will consist of four SKUs ranging from 16 core all the way to 64 core. Interestingly, all of them will feature 768MB of L3 cache which is just insane, and rather excessive for the lower-end SKUs. It’s possible that the final retail parts will disable part of the L3 cache on the lower-end, but the source hasn’t indicated anything of the sort.

| CPU Name | Cores/Threads | Base Clock | Boost Clock | L3 Cache (V-Cache + L3 Cache) | L2 Cache | TDP |

|---|---|---|---|---|---|---|

| AMD EPYC 7773X | 64/128 | 2.2 GHz | 3.5 GHz | 512 + 256 MB | 32 MB | 280W |

| AMD EPYC 7573X | 32/64 | 2.8 GHz | 3.6 GHz | 512 + 256 MB | 32 MB | 280W |

| AMD EPYC 7473X | 24/48 | 2.8 GHz | 3.7 GHz | 512 + 256 MB | 12 MB | 240W |

| AMD EPYC 7373X | 16/32 | 3.05 GHz | 3.8 GHz | 512 + 256 MB | 8 MB | 240W |

Looking at the specs, everything’s basically identical to the vanilla Milan parts, including the base and boost clocks, the TDP as well as the L2 cache (other than the crapton of L3 cache). This means that performance gains (as already indicated earlier) will vary from application to application, and won’t be much pronounced in every workload.

AMD Zen 5 Strix Point/Halo, Granite Ridge & Turin: Ryzen 9000 Specs, News & Rumors

AMD Zen 5 Strix Point/Halo, Granite Ridge & Turin: Ryzen 9000 Specs, News & Rumors AMD’s Zen 5 Being Sampled: Ryzen 9000 CPUs incl. Mobile Chips Launch Later This Year

AMD’s Zen 5 Being Sampled: Ryzen 9000 CPUs incl. Mobile Chips Launch Later This Year Intel 15th Gen Arrow Lake CPUs: Core Ultra 9 285K, Ultra 7 265K & Ultra 5 245K

Intel 15th Gen Arrow Lake CPUs: Core Ultra 9 285K, Ultra 7 265K & Ultra 5 245K Intel Core i9-13900K Performance Drop with Baseline Profile on B760 Boards Explored

Intel Core i9-13900K Performance Drop with Baseline Profile on B760 Boards Explored