Gigabyte’s internal documents were recently leaked by a hacker group. These contain a ton of info, but most of it is gibberish to the average consumer. However, they do contain plenty of interesting information as well. For example, details regarding AMD’s next-gen Epyc Genoa server processors, including specs, die-size, TDP, etc have also surfaced along with the breach.

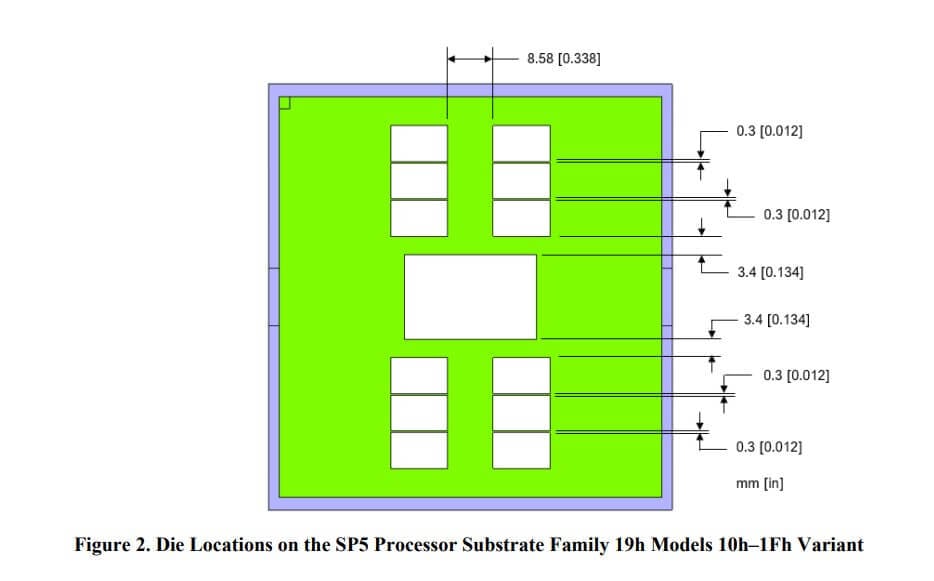

For starters, let’s have a look at the SP5 substrate diagram that will power the Epyc Genoa and succeeding lineups of AMD server products. As you can see, there are a total of 12 CCDs (each packing eight cores) and a large central I/O die. This results in a total core count of 96, as we’ve learned from previous rumors.

The documents also contain information regarding Zen 4 die sizes, such as the CCD and IOD. As per the leaked data, the Zen 4 CCD will have a die size of 10.70 x 6.75mm (area: 72.225mm2), while the IOD will be 24.79 x 16.0mm (area: 396.64mm2). Furthermore, the Epyc Genoa package will be 72.0 x 75.40mm (area: 5428mm2), with the SP5 LGA 6096 socket pushing 76.0 x 80.0mm (area: 6080mm2) .

Compared to the Zen 3 CCD, Zen 4 is 11% smaller (thanks to the 5nm node), with the IOD being 5% smaller than the 12nm IOD featured on Rome and Milan. AMD seems to have really pushed the package size with Genoa. We’re looking at a CPU with an area of 5,428 mm2, with the socket itself covering an area of 6,080 mm2. This explains why Genoa tops out at 96 cores.

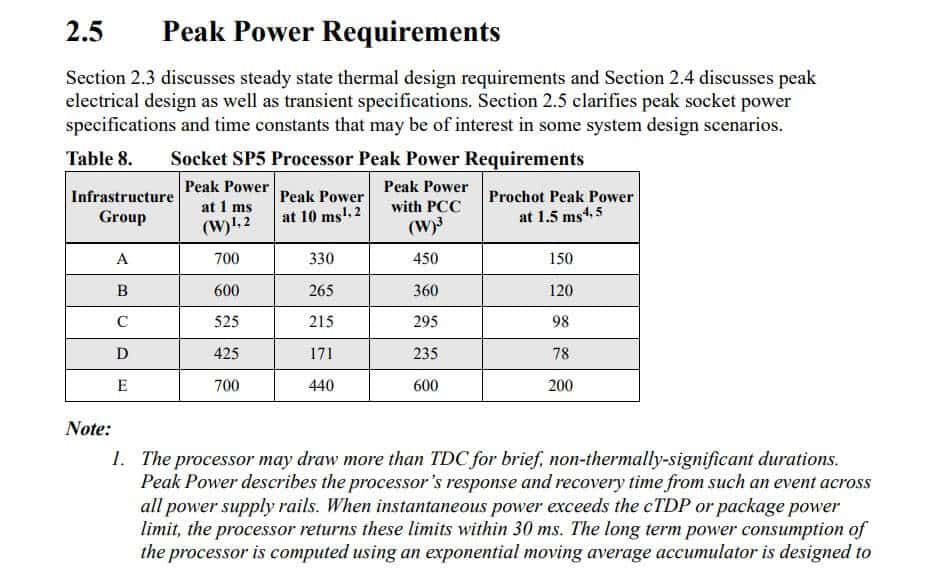

The TDP values of the SP5 socket have been significantly increased, and this may or may not be because of AVX-512 support. The default TDP of Genoa is pegged at 320W, with the option to push it to 400W. In comparison, Milan top out at 280W. We’re essentially looking at a TDP hike of 50% despite using a more advanced process node. The absolute max TDP for the socket is listed as 700W (for bursts of 1 ms), with the 10 ms max set to 440W. The peak power with PCC is listed as 600W.

Finally, the documents also state that Genoa will feature a total of 128 PCIe 5.0 lanes (yes, 5.0), DDR5-5200 memory, and up to 3 TB of DRAM. The memory will support up to 12 channels, with two DIMMs per channel.

Via: Yuko Yoshida