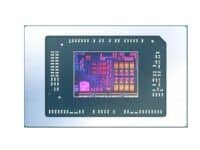

Intel’s Xe-HPG (DG2) specifications have surfaced (courtesy of Videocardz). The DG2 flagship will feature 512 EUs (as indicated by leaks) consisting of 16 Vector Engines and 16 Matrix Engines per Xe-Core in addition to a ray-tracing unit. The vector engines seem to feature two EUs each which in turn pack eight ALUs. I’m uncertain what the purpose of the Matrix Engines is.

They should be the equivalent of NVIDIA’s Tensor cores, designed for wider/longer instructions such as matrix multiplication. They are likely meant to power the XeSS upscaling technology, but this is pure speculation at this point. The Vector engines are 256-bit wide while the Matrix engines are a whopping 1024-bit wide, so I’m fairly confident in my predictions.

As reported last year, the DG2 features a large L2 cache, called the Memory Fabric. You can see a block diagram of the DG2 above. Going by Intel’s slide, it would seem that my prediction is correct. XeSS uses XMX and DP4a which confirms the use of advanced matrix instructions. XMX is for Tensor instructions while DP4a is meant for INT8 dot multiplications (for neural networking training).

XeSS is aimed at upscaling the image to 4K, with a performance target close to 1080p native rendering. We should get more details on this soon, so stay tuned.