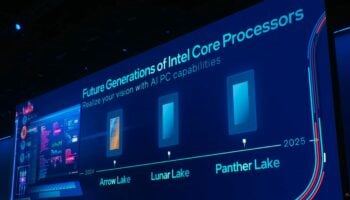

Intel seems to have slowed down its 3D packaging ambitions, with none of the coming two generations of Xeon Scalable processors slated to leverage Foveros (3D packaging introduced with Lakefield and to be employed in Meteor Lake client CPUs). In a recent presentation to investors, the chipmaker revealed that it won’t be using its 3D stacking technology in any of the foreseeable server designs (via: DylanPatel).

Clarification: While I can’t comment on the above report from Dylan Patel, Intel has informed us that it hasn’t abandoned Foveros. In fact, there are two different variants of 2nd Gen Foveros in the works. At the same time, the chipmaker didn’t specify which particular technology will be employed in Granite Rapids or whether it’ll use Foveros at all.

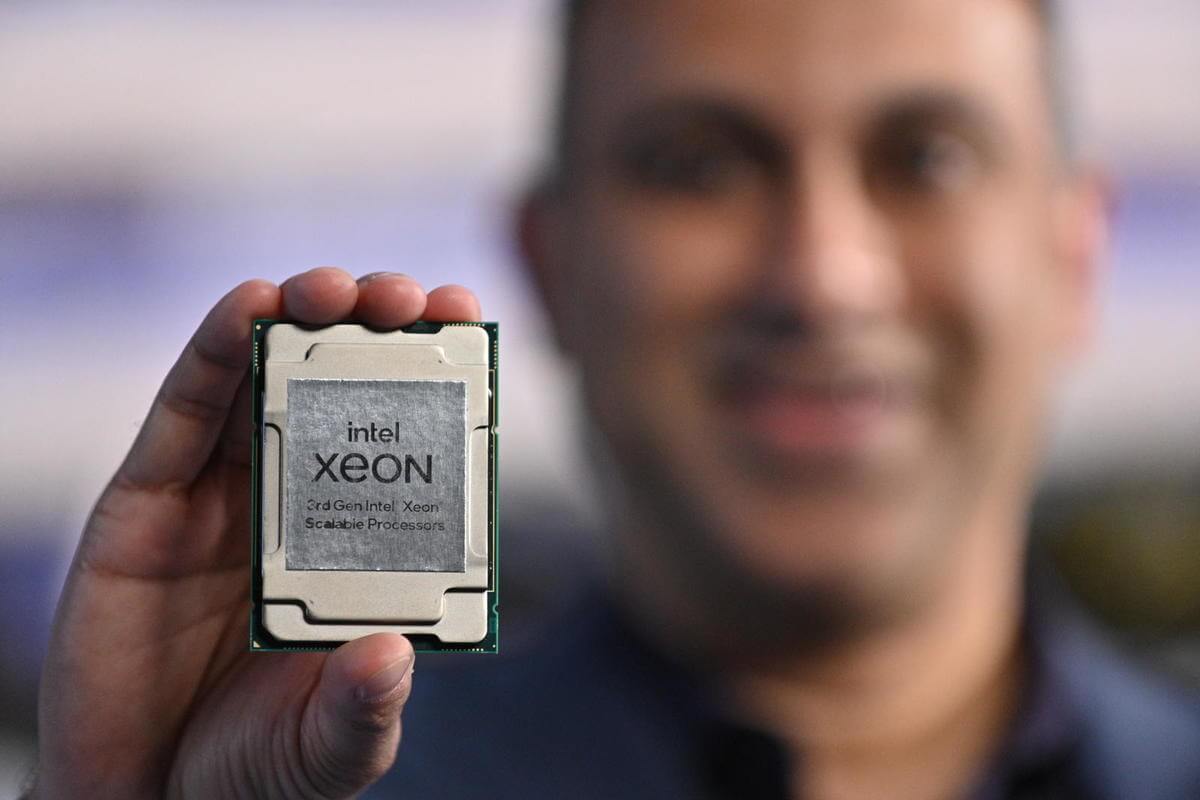

Sapphire Rapids is slated to be the first lineup from Intel to adopt the chiplet (MCM) or tiled design (plus some SKUs using on-die HBM) and Granite Rapids refining it. The former is expected to feature up to four (15-core, 1 disabled) tiles, resulting in a total core count of 56.

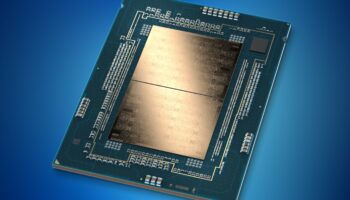

Granite Rapids-SP is expected to further increase both the tile and core count. The slides from the Intel Accelerated event show a total of eight tiles on the same substrate, including DRAM and possibly cache. The compute tiles look considerably larger than Sapphire Rapids, indicating an increase of (up to) 2x in core count. Granite Rapids will leverage the 7nm (Intel 4) node and be followed by Diamond Rapids in 2024.

| CPU Name | Cores/Threads | Base Clock | Boost Clock | L3 Cache (V-Cache + L3 Cache) | L2 Cache | TDP |

|---|---|---|---|---|---|---|

| AMD EPYC 7773X | 64/128 | 2.2 GHz | 3.5 GHz | 512 + 256 MB | 32 MB | 280W |

| AMD EPYC 7573X | 32/64 | 2.8 GHz | 3.6 GHz | 512 + 256 MB | 32 MB | 280W |

| AMD EPYC 7473X | 24/48 | 2.8 GHz | 3.7 GHz | 512 + 256 MB | 12 MB | 240W |

| AMD EPYC 7373X | 16/32 | 3.05 GHz | 3.8 GHz | 512 + 256 MB | 8 MB | 240W |

Meanwhile, AMD is planning to launch its Milan-X processors with 3D V-Cache technology by the end of the year. The specifications surfaced a while back. According to the source (@ExecuFix), Milan-X will consist of four SKUs ranging from 16 core all the way to 64 core. Interestingly, all of them will feature 768MB of L3 cache which is just insane, and rather excessive for the lower-end SKUs. It’s possible that the final retail parts will disable part of the L3 cache on the lower-end, but the source hasn’t indicated anything of the sort.