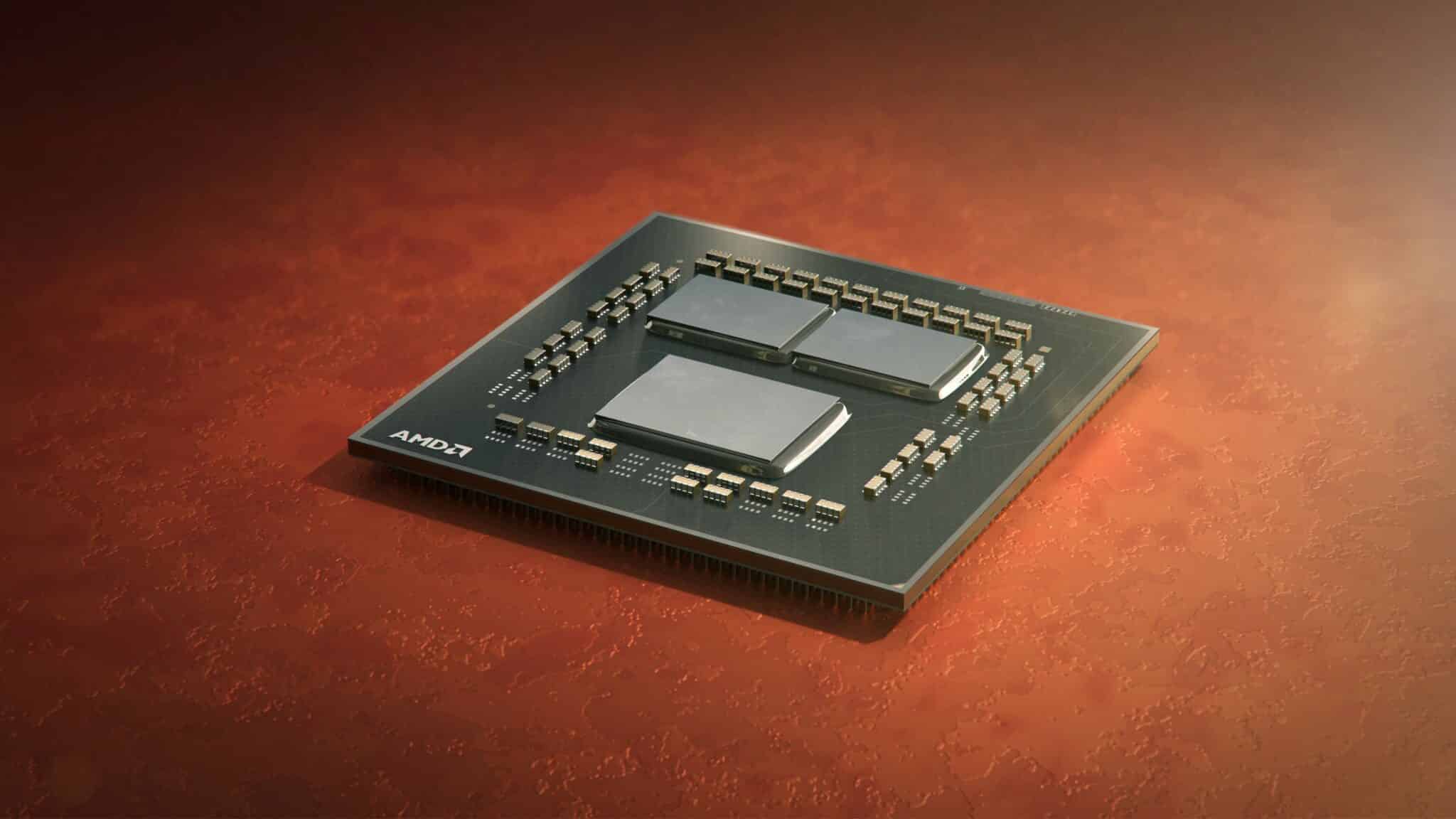

According to new information on the web, AMD’s first hybrid core architecture, codenamed “Strix Point” will feature Zen 5 cores as the high-performance cluster (big cores) and Zen 4D, a derivative of Zen 4 as the low power (small cores) cluster. Furthermore, the processor will leverage TSMC’s 3nm process which is expected since the targeted launch date for the SKU is sometime in late 2024, or early 2025.

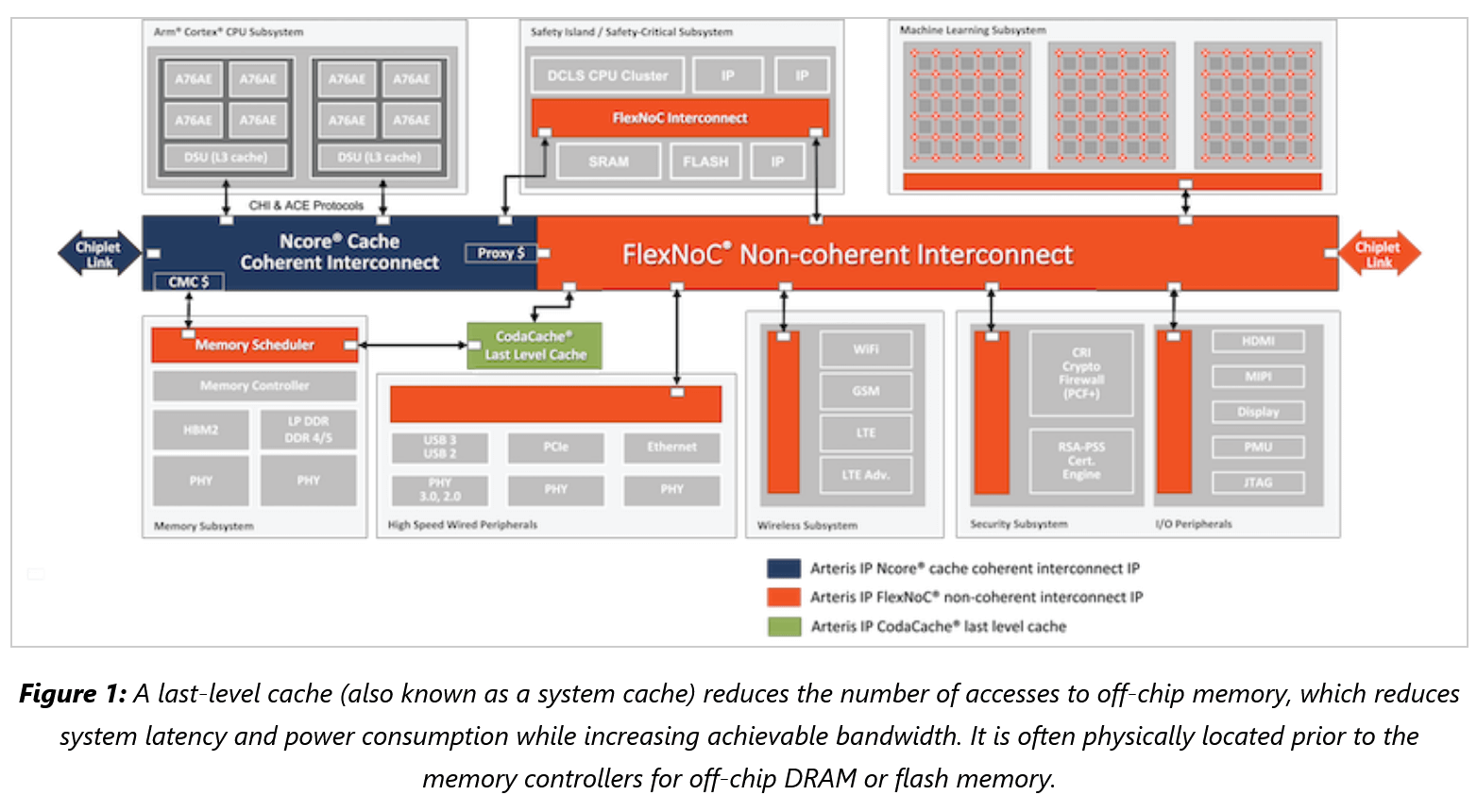

In addition to this, the Strix Point SoC will also feature an L4 cache in addition to L2 and L3 that will act as the system cache or last-level cache. The role of the system cache is to improve system latency and power draw by reducing the dependence on the DRAM and servicing as many requests from the higher levels caches as possible.

The software and the memory controller don’t “see” the LLC and therefore, it doesn’t require any kind of optimization from developers. Generally, it shouldn’t require any coherency hardware, but that may change depending on how AMD decides to implement it. Of course, this will require extra die size but looking at modern packaging technologies, we might see it stacked above regular compute dies or something similar.

Lastly, it’s not certain whether AMD will bring a hybrid core architecture to both mobile and desktop platforms as the latter doesn’t benefit much from it. The low-power mobile (15W) and high-performance mobile (45W) should however get this treatment.