As the year 2021 comes to an end, we look forward to what 2022 has to offer. In the GPU space, we’ll be seeing quite a bit of activity. From NVIDIA’s RTX 40 series “Ada Lovelace” GPUs to AMD’s chiplet based RDNA 3 parts, and Intel’s Arc “Alchemist” lineup, the PC gaming market will see some major shifts in 2022. Out of these, only the Radeon offerings will feature an MCM design, along with 3D stacking, marking another milestone in AMD’s long history.

Well-reputed leaker on AMD’s chips @Greymon55 has shared his speculated specifications of the RDNA 3 dies. Going by these numbers, it looks like both the Navi 31 and Navi 32 dies will feature a dual-chiplet design. The Radeon RX 7900 XT will feature up to 15,360 shaders across 60 Work Group Processors (WGPs) paired with 16GB of GDDR6 memory across a 256-but bus. The L3 “Infinity” Cache will be increased to 256MB, 3D stacked upon the primary compute die. The GPU core will run at around 2.5GHz, the same as Navi 21 which is a bit surprising if it’s fabbed on TSMC’s N5 node (might be N6 to improve supply). Overall, Navi 31 should easily be 2.2-2.5x faster than its predecessor, with the RX 7800 XT beating the RX 6800 XT by up to 50%.

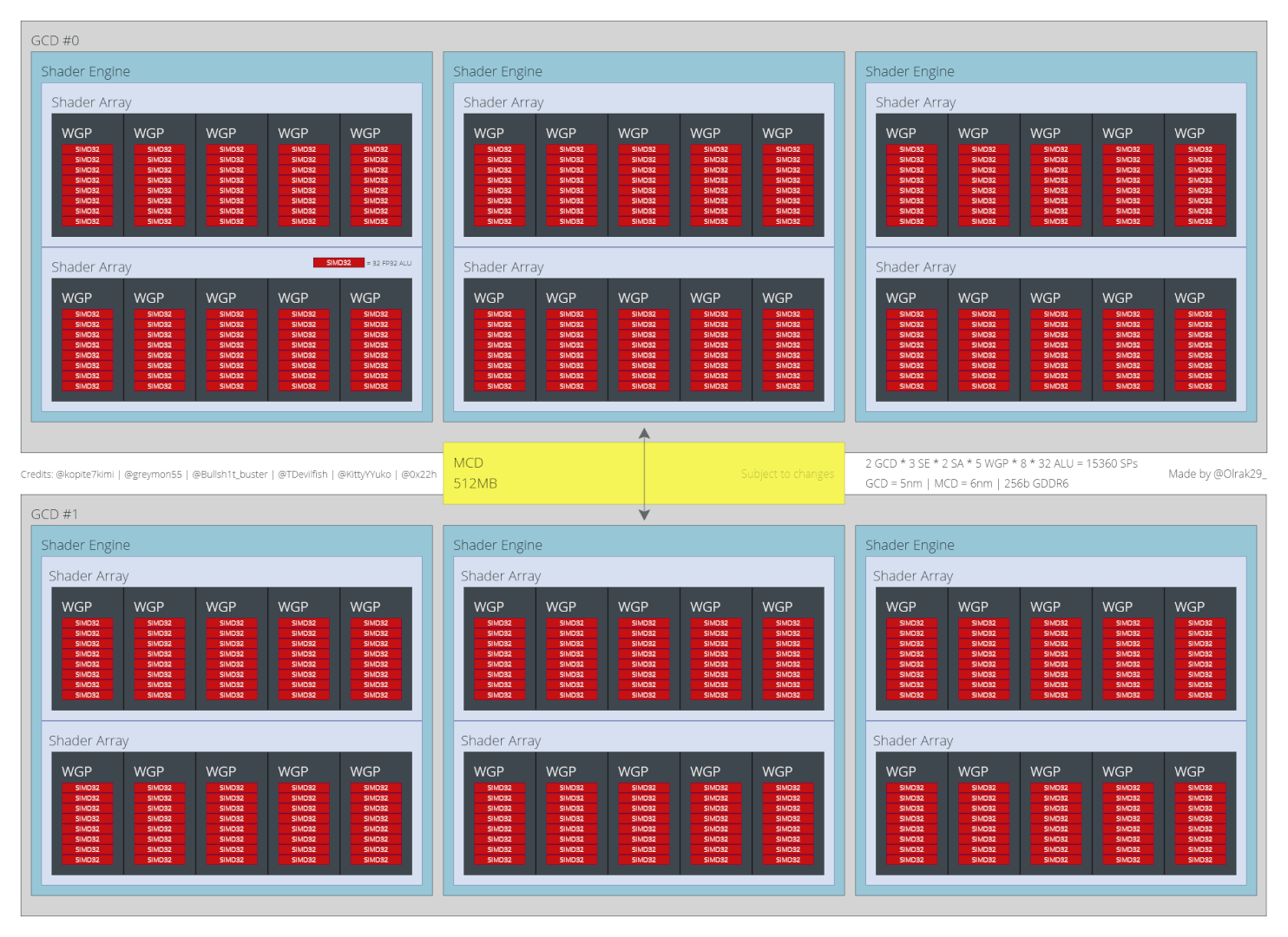

Each Graphics Die (GCD) features three Shader Engines which are made up of two Shader Arrays each. In turn, each Shader Array packs five WGPs containing eight SIMD units (vs four on RDNA 2). The two dies are connected by a bridge interconnect paired with 256MB of L3 “Infinity” Cache. According to the source, the GCDs will be fabbed on TSMC’s 5nm (N5) node while the MCD will be fabbed on the older 6nm (N6) node. Each die should come with a 128-bit bus (divided into eight controllers), resulting in an overall bus width of 256-bit and the same external bandwidth of 448GB/s as the RX 6800 XT/6900XT.

AMD’s RDNA 3 graphics architecture is expected to get a major overhaul at the front-end, with redesigned Work Group Processors in place of Compute Units, or Dual Compute Units. With RDNA 1 and 2, the WGPs were the basic units for workload scheduling (from CUs on GCN/Vega), but it looks like that is going to change again with Navi 3x. Dual Compute Units are being discarded in favor of wider Work Group Processors, packing as many as 256 stream processors across eight 32-wide SIMDs.

In comparison, Navi 21 featured a Shader Engine packing 10 Dual Compute Units (20 Compute Units) which was in turn divided into two SIMDs per CU or four per DCU. Each CU featured its own vector and scalar units, along with a ray-accelerator, texture mapping units, registers, and cache. Scheduling was done on a WGP (DCU) basis, meaning four wave32 workgroups were assigned at a time. With Navi 3x, scheduling will become more complex as you’re taking 8 SIMDs or wave32 workgroups into account at once.

Navi 32 is also going to be a chiplet design with two compute dies and one MCD. It’ll likely power the Radeon RX 7700 XT. We’re looking at a core count of around 10,240 shaders (or 40WGP), and a bus width of 192-bit paired with 12GB of GDDR6 memory. The L3 “Infinity Cache” is most likely going to be cut down to 192MB 3D stacked atop the compute die. The GPU core will run between 2.6-2.8GHz. The Radeon RX 7700 XT should be around 1.5-2x faster than 6700 XT, with roughly the same power draw.

Navi 33 will pack 4096 shaders (stream processors) across 16 WGPs. It’s expected to power the Radeon RX 7600 XT, making it a massive upgrade over the existing Radeon RX 6600 XT and its 2,304 shaders. We’re looking at an increase of more than 2x if you include the IPC, compute, and frequency gains. The Radeon RX 7600 XT is expected to pack 64MB of Infinity Cache. Rumors indicate a monolithic design, with four 32-bit memory controllers for an overall bus width of 128-bit paired with 8GB of GDDR6 memory. The Navi 33 core will run at up to 3GHz, with AIB models potentially being even faster.